- ubuntu12.04环境下使用kvm ioctl接口实现最简单的虚拟机

- Ubuntu 通过无线网络安装Ubuntu Server启动系统后连接无线网络的方法

- 在Ubuntu上搭建网桥的方法

- ubuntu 虚拟机上网方式及相关配置详解

CFSDN坚持开源创造价值,我们致力于搭建一个资源共享平台,让每一个IT人在这里找到属于你的精彩世界.

这篇CFSDN的博客文章Cortex M架构与Cortex A架构中断系统的区别由作者收集整理,如果你对这篇文章有兴趣,记得点赞哟.

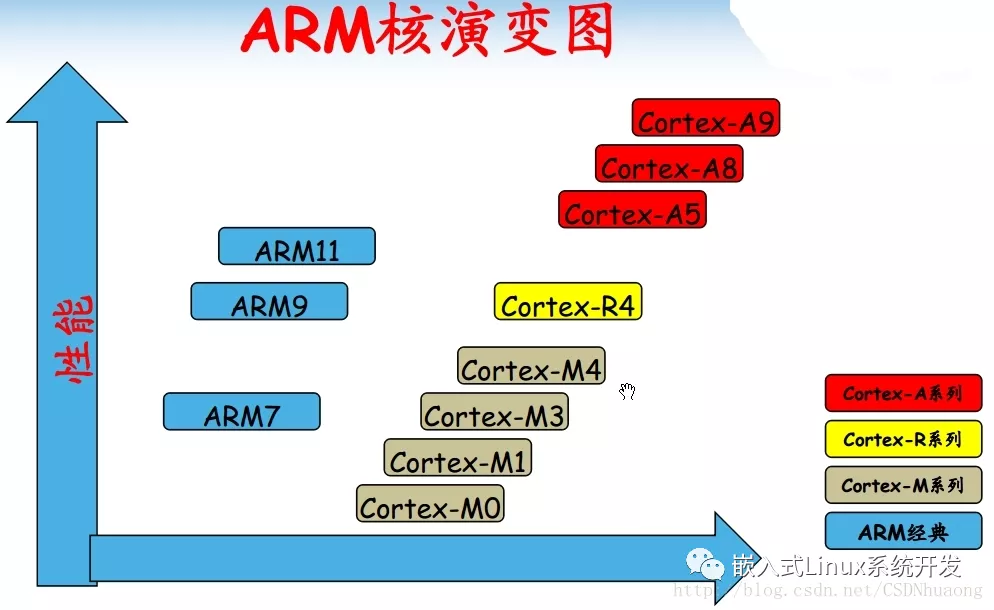

Cortex M架构,典型就是STM32系列,比如STM32F103(Cortex M3).

Cortex A架构,可以细分为Cortex A7,Cortex A8,Cortex A9,Cortex A15等,比如NXP的IMX6系列,TI的AM335X系列等.

Cortex M主要用在微控制器领域,Cortex R主要用在对实时性要求比较高的领域,Cortex A主要用在高端应用领域.

。

在Cortex M架构中,比如STM32F103,中断向量表是写在启动文件当中,一般为startup_stm32f10x_hd.s或者startup_stm32f10x_md.s中,.s结尾为汇编文件,这个汇编语言写的启动文件的作用,是在板子上电后为C语言代码的运行做好初始化工作,比如设置堆栈大小,设置中断向量表等,然后再跳转到main函数去执行你的C代码。文件内容如下(部分省略):

设置栈大小 。

设置堆大小 。

; Vector Table Mapped to Address 0 at Reset后面很多 DCD 的就是STM32的中断向量表,系统所有可用的中断都写在这里,包括外部中断、定时器中断、DMA中断、IIC中断、串口中断等.

其中“__initial_sp”就是第一条中断向量,存放的是栈顶指针,接下来是第 2 行复位中断复位函数Reset_Handler 的入口地址,依次类推,直到最后一个中断服务函数DMA2_Channel4_5_IRQHandler 的入口地址,这样 STM32F103 的中断向量表就建好了.

。

先配置好中断向量表(自动),然后配置一下IO口,配置NVIC来管理中断,使能中断,最后编写中断服务函数,中断服务函数里是我们真正想做的事情.

这个思路也适合于Cortex A架构,只是中断系统不同,中断管理器也不同,STM32中的中断管理器是NVIC,Cortex A架构的中断管理器是GIC控制器。GIC 是 ARM 公司给 Cortex-A/R 内核提供的一个中断控制器.

。

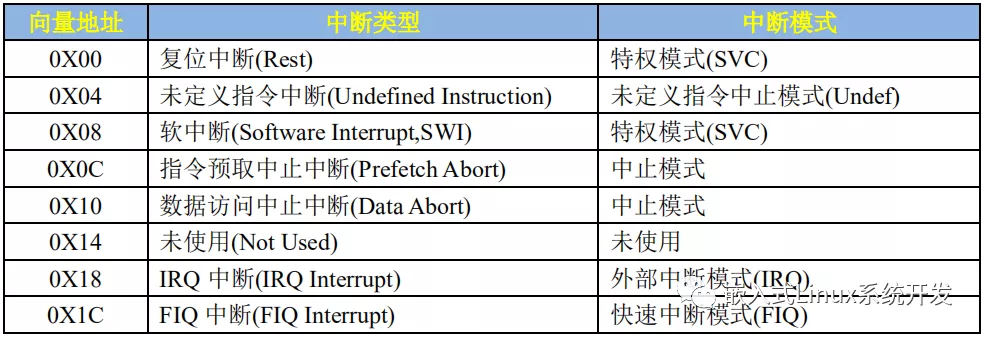

下表为Cortex A架构中断向量表,这个表也是写在.s结尾的启动文件当中,为C语言代码的运行提供前期的初始化工作,只有做好了初始化,你的C语言代码才会运行,启动文件中做好初始化以后,会跳转到你的main函数.

可以发现比STM32的中断少了很多,只有八个中断,还有一个未使用。其中我们最常用的中断是复位中断和 IRQ 中断.

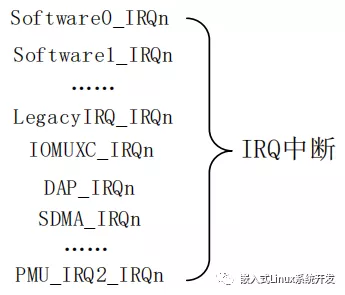

实际上Cortex A架构是不可能只有这么少的中断,Cortex-A 内核 CPU 的所有外部中断都属于IQR 中断,当任意一个外部中断发生的时候都会触发 IRQ 中断。在 IRQ 中断服务函数里面就可以读取指定的寄存器来判断发生的具体是什么中断,进而根据具体的中断做出相应的处理,如下图:

。

1、复位中断(Rest),CPU 复位以后就会进入复位中断,我们可以在复位中断服务函数里面做一些初始化工作,比如初始化 SP 指针、DDR 等等.

2、未定义指令中断(Undefined Instruction),如果指令不能识别的话就会产生此中断.

3、软中断(Software Interrupt,SWI),由 SWI 指令引起的中断,Linux 的系统调用会用 SWI指令来引起软中断,通过软中断来陷入到内核空间.

4、指令预取中止中断(Prefetch Abort),预取指令的出错的时候会产生此中断.

5、数据访问中止中断(Data Abort),访问数据出错的时候会产生此中断.

6、IRQ 中断(IRQ Interrupt),外部中断,芯片内部的外设中断都会引起此中断的发生.

7、FIQ 中断(FIQ Interrupt),快速中断,如果需要快速处理中断的话就可以使用此中.

。

中断向量表都是链接到代码的最前面,比如一般 ARM 处理器都是从地址 0X0000 0000 开始执行指令的,那么中断向量表就是从0X0000 0000 开始存放的.

在STM32中,一般代码是下载到 0X0800 0000开始的存储区域中。因此中断向量表是存放到 0X0800 0000 地址处的,而不是 0X00000000。这种是通过中断向量表偏移实现的.

原文地址:https://mp.weixin.qq.com/s/PENYZoTIKYHOhCdCQhCd7A 。

最后此篇关于Cortex M架构与Cortex A架构中断系统的区别的文章就讲到这里了,如果你想了解更多关于Cortex M架构与Cortex A架构中断系统的区别的内容请搜索CFSDN的文章或继续浏览相关文章,希望大家以后支持我的博客! 。

Cortex M23/33 的 TrustZone 和 Cortex A 的 TrustZone 有什么区别?我可以开始在 Cortex A 处理器上构建我的 Cortex M23 应用程序原型(pr

Cortex-M3 的初始堆栈指针值位于 0x0 且复位处理程序位于 0x4 的原因是什么?这样做的设计理由是什么? 为什么 ARM 人员不能像对待 Cortex-A 那样将 0x0 留给重置处理程序

为一家公司构建的 Cortex A5 编写的代码能否轻松移植到另一家公司构建的 Cortex A9 上? 我想编写一些在 Atmel 的 SAMA5D4 上运行的裸机 C 代码(Cortex A5),

我决定按照本指南在 XU4 上编译 Qt5.8: http://freecode.hu/sbcomp/2016/08/15/compiling-qt-5-8-on-odroid-xu4/但在第 4 步

我正在使用 Sourcery CodeBench Lite 2012.03-56 编译器和 gdb 套件 texane gdb server . 今天我想尝试使用便宜的 STM32VLDISCOVER

我想知道ARM内核(Cortex-A系列处理器)访问内存的顺序?从内核生成的虚拟地址到内存,再从内存传输指令/数据到内核。考虑核心已经为一些数据/指令生成了一个虚拟地址并且 TLB 有一个未命中,那么

据我了解,Cortex M0/M3 处理器只有一个存储空间来保存指令和数据,并且只能通过内存总线接口(interface)进行访问。因此,如果我理解正确,处理器必须在每个时钟周期读取一条新指令才能进入

Cortex-A57 优化指南指出,大多数在 128 位向量数据上运行的整数指令可以双发出(第 24 页,整数基本 F0/F1,逻辑 F0/F1,执行吞吐量 2)。 然而,根据我们的内部(综合)基准测

很难说出这里问的是什么。这个问题是含糊的、模糊的、不完整的、过于宽泛的或修辞性的,无法以目前的形式得到合理的回答。如需帮助澄清此问题以便重新打开它,visit the help center 。 已关

我正在使用 Cortex管理一些用于 React 应用程序的数据。 Cortex's API listing列出了一些只存在于数组上的方法,即 filter 和 find。 给定一个对象: var s

我有一个 KL17,我正在尝试编写一个引导加载程序以允许 OTA 更新。我无法跳转到用户应用程序,这就是我正在尝试的。 void JumpToUserApplication(uint32_t user

我正在尝试调试基于运行 FreeRTOS 的 STM32F3 uC 的应用程序。我已在应用程序的线程上下文中的随机位置手动将 PSP 设置为无效值(例如 0),希望触发 memManageFault/

我有一个关于在 cortex m3 中使用信号量的问题。我发现了一个线程“ARM cortex:mutex using bit banding”ARM cortex: mutex using bit

我已经阅读了有关 Cortex-M3(或 M0)的 ARM 文档,它说它可以用作 NVIC Controller 内的电平感应或脉冲(边沿)中断。问题是,如果这是通过软件完成的,那么如何做到这一点相当

Cortex M架构,典型就是STM32系列,比如STM32F103(Cortex M3)。 Cortex A架构,可以细分为Cortex A7,Cortex A8,Cortex A9,Cor

我正在尝试通过编写自己的启动代码和链接器脚本来学习 ARM 处理器的启动过程。我使用的芯片是LPC810,我遵循了http://midibel.com/blink0.html中的示例, 两个例子都在我

有一个比较: if( val0 > val1 ) 其中val0和val1是双变量。 Apple LLVM编译器生成的代码是 +0x184 vcmpe.f64

在 ARM documentation ,它提到 The Cortex-M4 processor supports ARMv7 unaligned accesses, and performs all

我或多或少有关于 Cortex-M 异常(IRQ 中断)的理论问题。假设我们有两个由同一外部信号触发的外部中断 PINT0 和 PINT1。两个中断(在 NVIC 寄存器 IPR0 中)设置相同的优先

我编写了(IMO)几乎最简单的 ARM 应用程序,但它不起作用:)可能出什么问题了?错过了什么? 闪存写入和 CPU 复位后,寄存器中存在垃圾。 请友善,如果你知道,请告诉我必须做什么才能运行最简单的

我是一名优秀的程序员,十分优秀!