- html - 出于某种原因,IE8 对我的 Sass 文件中继承的 html5 CSS 不友好?

- JMeter 在响应断言中使用 span 标签的问题

- html - 在 :hover and :active? 上具有不同效果的 CSS 动画

- html - 相对于居中的 html 内容固定的 CSS 重复背景?

关闭。这个问题是off-topic .它目前不接受答案。

想改善这个问题吗? Update the question所以它是 on-topic对于堆栈溢出。

8年前关闭。

Improve this question

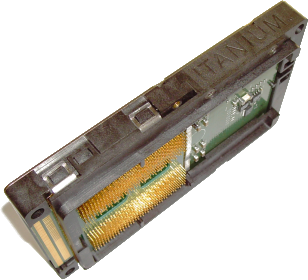

在 this article Jonh Dvorak 将安腾称为“过去 50 年中最伟大的失败之一”。虽然他描述了过度乐观的市场预期和这个想法的戏剧性财务结果,但他并没有深入探讨这个史诗般的失败的技术细节。我有机会使用安腾一段时间,我个人喜欢它的架构,与现代 x86 处理器架构相比,它是如此清晰、简单和直接……

那么它失败的技术原因是什么?表现不佳?与 x86 代码不兼容?编译器的复杂性?为什么这个“Itanic”会沉没?

最佳答案

Itanium 失败了,因为 VLIW 对于当今的工作负载简直是一个糟糕的主意。

Donald Knuth,广受尊敬的计算机科学家,said in a 2008 interview认为““安腾”方法 [本来] 非常棒——直到结果发现,人们想要的编译器基本上是不可能写出来的。”1

这几乎解决了问题。

对于科学计算,每个基本块至少有几十条指令,VLIW 可能工作正常。那里有足够的说明来创建好的包。对于更现代的工作负载,通常每个基本块大约有 6-7 条指令,但事实并非如此(这是 SPEC2000 的平均值,IIRC)。编译器根本找不到独立的指令来放入包中。

现代 x86 处理器,除了 Intel Atom(前 Silvermont)和我相信 AMD E-3**/4**,都是乱序处理器。它们维持一个大约 100 条指令的动态指令窗口,并在该窗口内在输入准备就绪时执行指令。如果多个指令准备好运行并且它们不竞争资源,它们将在同一个循环中一起运行。

那么这与 VLIW 有何不同? VLIW 和乱序之间的第一个关键区别是乱序处理器可以从不同的基本块中选择指令同时执行。这些指令无论如何都是推测执行的(主要基于分支预测)。第二个关键区别是无序处理器动态确定这些调度(即,每个动态指令都是独立调度的;VLIW 编译器对静态指令进行操作)。

第三个关键区别是,无序处理器的实现可以随心所欲,而无需更改指令集(英特尔酷睿有 5 个执行端口,其他处理器有 4 个,等等)。 VLIW 机器可以并且确实一次执行多个包(如果它们不冲突)。例如,early Itanium CPUs execute up to 2 VLIW bundles per clock cycle, 6 instructions ,后来的设计 (2011's Poulson and later) 最多运行 4 个包 = 每个时钟 12 条指令,SMT 从多个线程获取这些指令。在这方面,真正的 Itanium 硬件就像传统的有序超标量设计(如 P5 Pentium 或 Atom),但编译器有更多/更好的方式向硬件公开指令级并行性(理论上,如果它可以找到够了,这就是问题所在)。

在性能方面具有相似的规范(缓存、内核等),他们只是击败了安腾。

那么为什么现在要购买安腾呢?好吧,唯一的原因确实是 HP-UX。如果您想运行 HP-UX,那就是这样做的方法...

许多编译器作者不这么看——他们总是喜欢 Itanium 给他们更多的事情做,让他们重新控制等等。但他们不会承认它失败的惨状。

脚注 1:

这是对多核处理器值(value)的回应的一部分。 Knuth 说并行处理很难利用;在编译时为 VLIW 找到并公开细粒度指令级并行性(和显式推测:EPIC)也是一个难题,并且与寻找粗粒度并行性以将顺序程序或函数拆分为多个线程以自动进行充分利用多核。

11 年后他仍然基本正确:对于大多数非服务器软件来说,每线程性能仍然非常重要,这是 CPU 供应商所关注的,因为许多内核是不可替代的。

关于hardware - "Itanium fiasco"背后的技术原因是什么(如果有的话)?,我们在Stack Overflow上找到一个类似的问题: https://stackoverflow.com/questions/1011760/

我对cassandra并使用1.2.10非常陌生。我有一个时间戳数据类型的主键列。现在,我正在尝试检索日期范围的数据。由于我们知道不能在cassandra中使用,因此我使用的是大于()来获取日期范围。

我正在尝试进行有条件的转场。但我得到: Terminating app due to uncaught exception 'NSInvalidArgumentException', reas

我有一个游戏项目,在调试和发布模式下在设备上运行得非常好。我有两个版本。旧版本和新版本具有更多(后来我添加了)功能,并且两者的 bundle ID、版本相同。当我构建旧版本时,之前没有安装“myGam

这个问题已经有答案了: 奥 git _a (2 个回答) 已关闭 5 年前。 我正在获取 ClassCastException 。这两个类来自不同的 jar,但是JettyContinuationPr

以下代码行抛出异常: HttpResponse response = client.execute(request); // actual HTTP request 我能够捕获它并打印: Log

就目前情况而言,这个问题不太适合我们的问答形式。我们希望答案得到事实、引用资料或专业知识的支持,但这个问题可能会引发辩论、争论、民意调查或扩展讨论。如果您觉得这个问题可以改进并可能重新开放,visit

public class TwoThreads { private static Object resource = new Object(); private static void

当我输入 6 (int) 作为值时,运行此命令会出现段错误 (gcc filename.c -lm)。请帮助我解决这个问题。预期的功能尚未实现,但我需要知道为什么我已经陷入段错误。 谢谢! #incl

所以,过去一周半我一直在研究这个 .OBJ/.MTL 网格解析器。在这段时间里,我一直在追踪/修复很多错误、清理代码、记录代码等等。 问题是,每修复一个错误,仍然会出现这个问题,而且一张图片胜过一千个

我正在运行一个代码,它基本上围绕 3 个维度旋转一个大数据数组(5000 万行)。但是,我遇到了一个奇怪的问题,我已将其缩小到如何评估旋转矩阵。基本上,对于除绕 x 轴以外的任何旋转,python 代

就在你说这是重复之前,我已经看到了其他问题,但我仍然想发布这个。 所以我正在阅读 Thinking in Java -Bruce Eckel 这篇文章是关于小写命名约定的: In Java 1.0 a

我想在我的应用程序中使用 REST API。它为我从这个应用程序发出的所有请求抛出 SocketTimeoutException。 Logcat 输出:(您也可以在此处看到带有漂亮格式的输出:http

我知道 raise ... from None 并已阅读 How can I more easily suppress previous exceptions when I raise my own

在未能找到各种Unix工具(例如xargs和whatnot)的最新独立二进制文件(this version很好,但需要外部DLL)后,我承担了自己进行编译的挑战。 ...这是痛苦的。 最终,尽管如此,

我有一个用PHP编写的流套接字服务器。 为了查看一次可以处理多少个连接,我用C语言编写了一个模拟器来创建1000个不同的客户端以连接到服务器。 stream_socket_accept几次返回fals

我的Android Studio昨天运行良好,但是今天当我启动Android Studio并想在移动设备上运行应用程序时,发生了以下错误, 我在互联网和stackoverflow上进行了搜索,但没有解

默认情况下,grails似乎为Java域对象的toString()返回:。那当然不是我想要的,所以我尝试@Override toString()返回我想要的。当我尝试grails generate-a

尝试通过LDAP通过LDAP对用户进行身份验证时,出现以下错误。 Reason: Cannot pass null or empty values to constructor. 谁能告诉我做错了什么

我正在尝试使用应用程序附带的 Houdini Python 模块,该模块是 Houdini 安装文件夹的一部分,位于标准 Python 路径之外。按照安装说明操作后,运行 Houdini Termin

简单地说,我正在为基本数据库编写单链表的原始实现。当用户请求打印索引下列出的元素高于数据库中当前记录数量时,我不断出现段错误,但仅当差值为 1 时。对于更高的数字,它只会触发我在那里编写的错误系统。

我是一名优秀的程序员,十分优秀!