作者热门文章

- Java锁的逻辑(结合对象头和ObjectMonitor)

- 还在用饼状图?来瞧瞧这些炫酷的百分比可视化新图形(附代码实现)⛵

- 自动注册实体类到EntityFrameworkCore上下文,并适配ABP及ABPVNext

- 基于Sklearn机器学习代码实战

sdram包含两个部分:sdram_ctrl、fifo_ctrl.

SDRAM在上电后首先需要执行初始化操作,才可执行其他操作.

配置寄存器模式 。

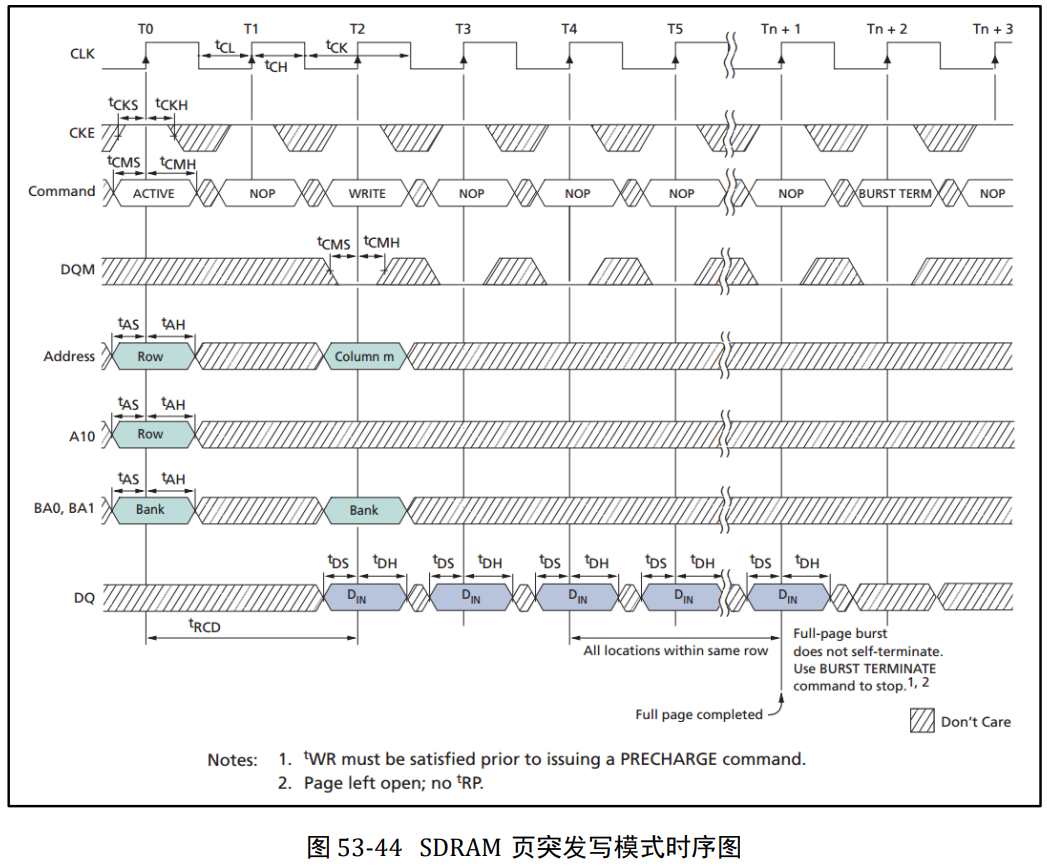

潜伏期为三个周期 。

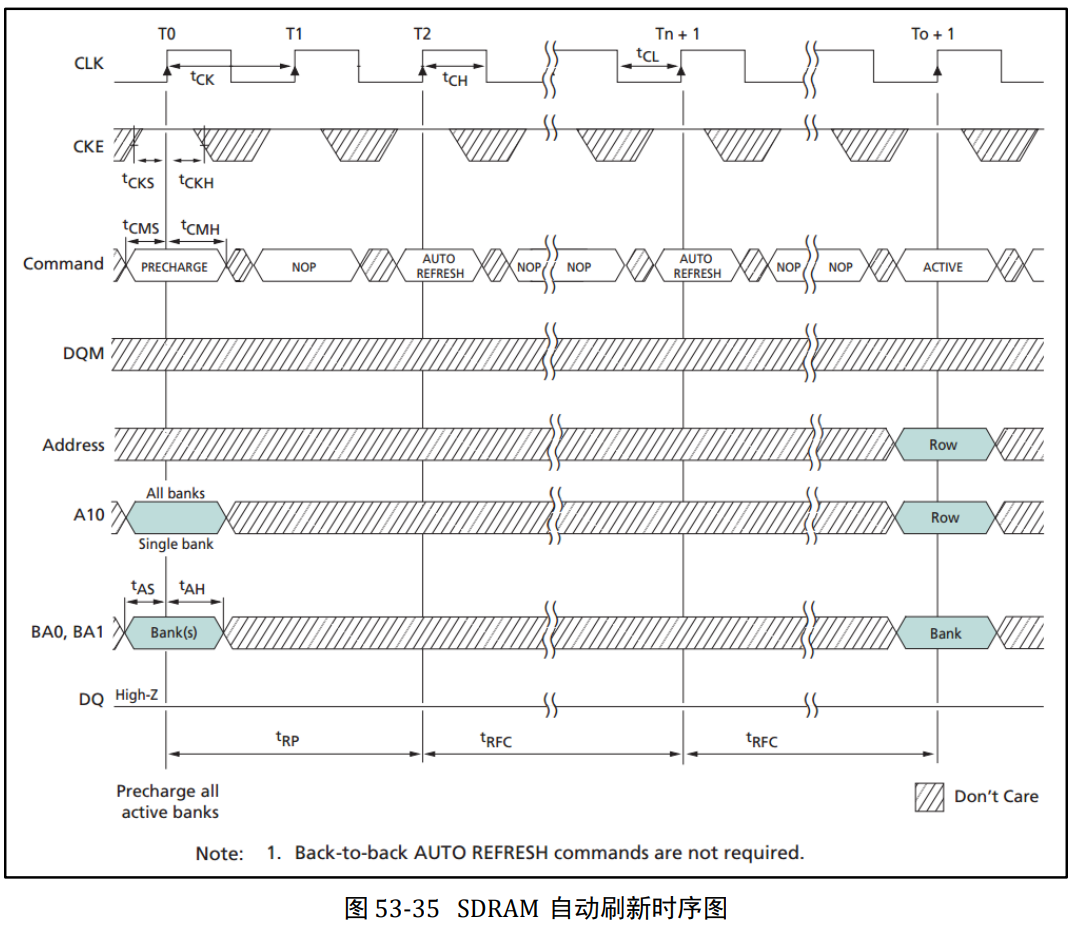

突发长度为页突发 。

突发类型为顺序类型 。

写模式为页突发写模式 。

信号操作:

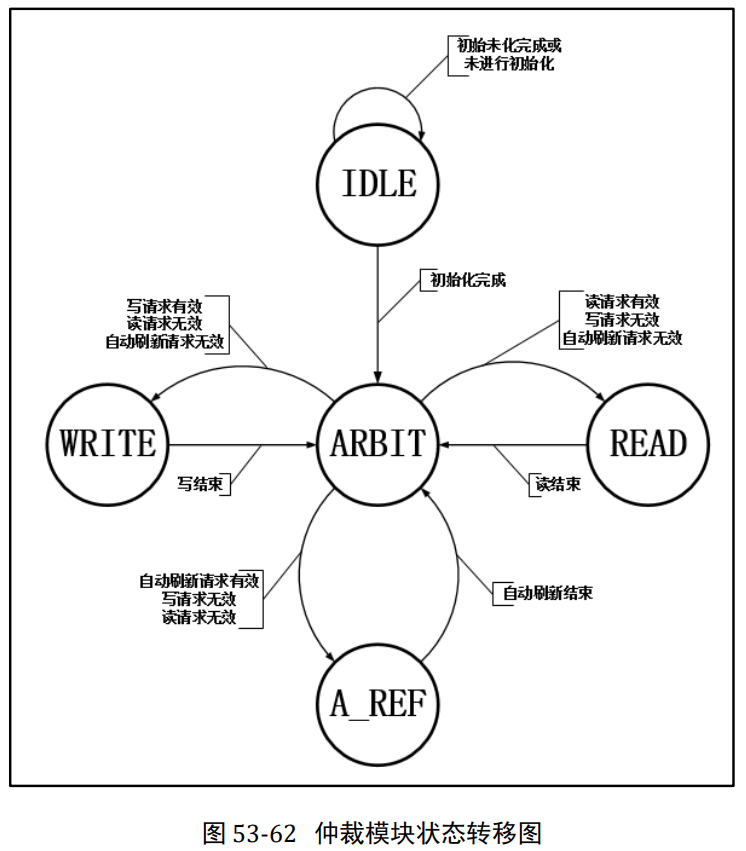

总体采用状态机来设计,分为以下几个状态:

为了防止亚稳态的产生,状态机编码均使用格雷码 。

跳转条件使用计数器进行计数完成判断 。

另外为了跳转操作代码简洁,声明组合逻辑的信号完成各个状态的跳转 。

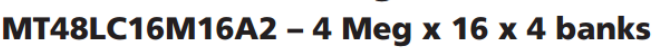

由于自动刷新信号需要重复进行,因此使用计数器完成自动刷新操作计数 。

最终按照各个状态完成输出信号的幅值,注意使用的为时序逻辑,因此输出相比状态跳转延迟一拍 。

最后此篇关于基于FPGA的SDRAM控制器的文章就讲到这里了,如果你想了解更多关于基于FPGA的SDRAM控制器的内容请搜索CFSDN的文章或继续浏览相关文章,希望大家以后支持我的博客! 。

我正在研究 TM4C1294 + ccs 6.0.1 + TI 5.1.9(编译器)。 在 8MB 外部 sdram 中读取/写入变量工作正常,例如 g_pui16EPISdram = (uint16

如何保留 SDRAM 的一部分,比如 4 个字节,在 U-Boot 和 Linux 内核之间传递一个标志,以便链接器不会初始化这个保留的内存位置,并且在热启动后保留该值?我试图避免使用引导参数来最大限

我想在 Cyclone-V 中的 HPS 和 FPGA 之间共享内存。我在Qsys(Platform Designer)中用avalon master和所有东西实例化了“sdram_slave”接口(

我是一名优秀的程序员,十分优秀!