- Java锁的逻辑(结合对象头和ObjectMonitor)

- 还在用饼状图?来瞧瞧这些炫酷的百分比可视化新图形(附代码实现)⛵

- 自动注册实体类到EntityFrameworkCore上下文,并适配ABP及ABPVNext

- 基于Sklearn机器学习代码实战

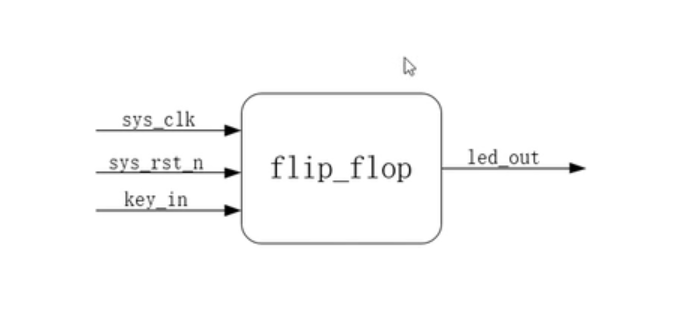

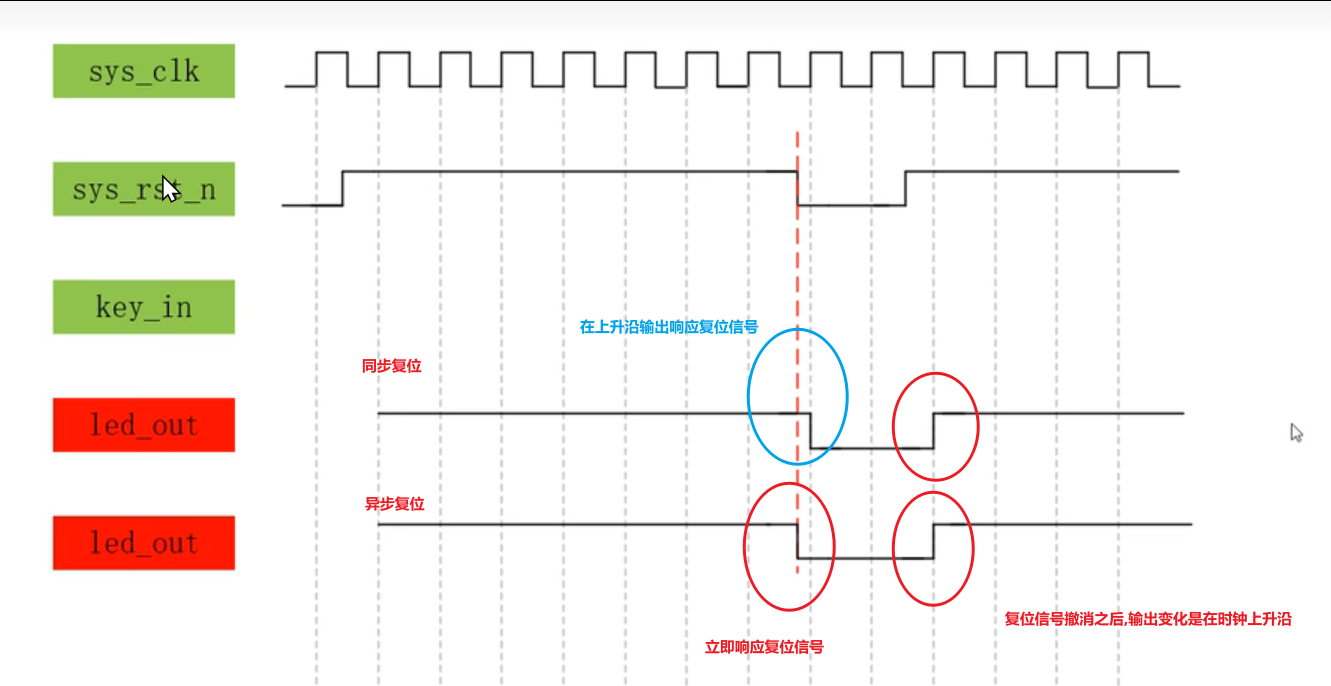

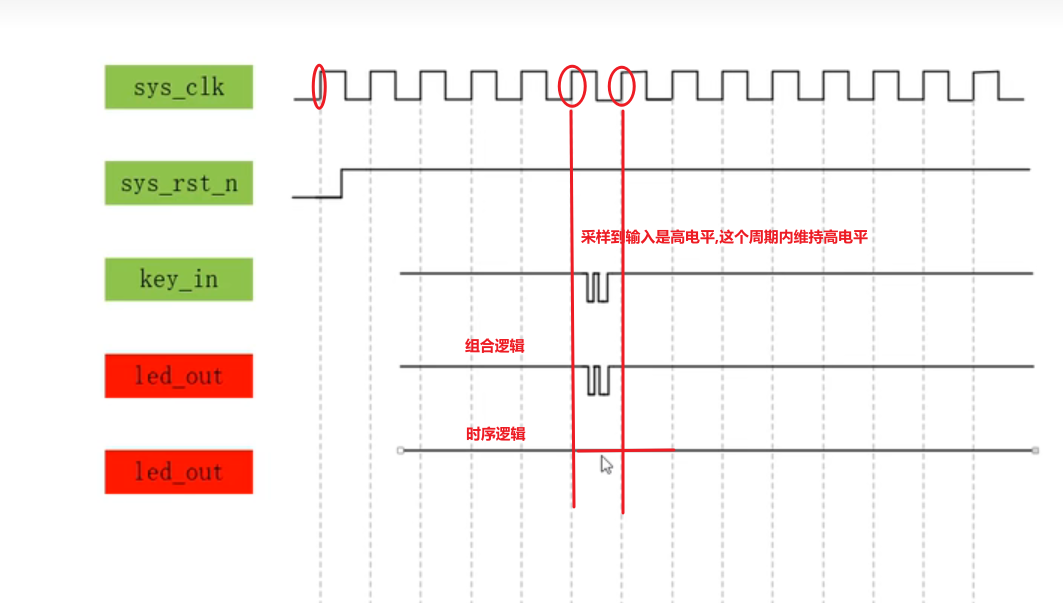

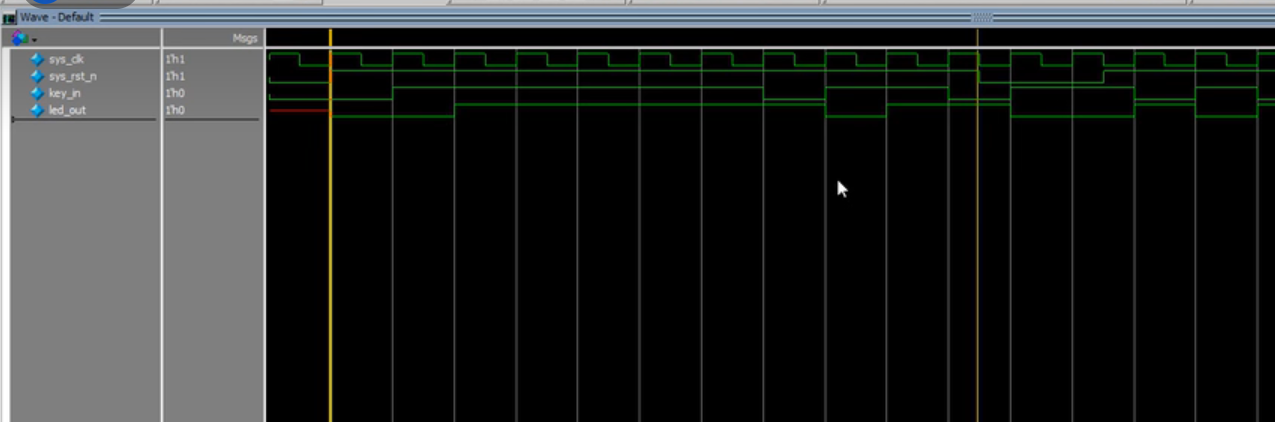

组合逻辑存在一个最大的缺点就是存在竞争与冒险,系统会产生不定态;使用时序逻辑电路就会极大的改善这种情况 寄存器具有存储功能,一般是由D触发器构成,由时钟脉冲控制,每个D触发器能够存储一位二进制码 D触发器工作原理: 在一个脉冲信号(一般为晶振产生的时钟脉冲)上升沿或者是下降沿作用下,将信号从输入端D送到输出端Q,如果时钟脉冲的边沿信号未出现,即使输入信号改变,输出信号仍保持原来的值 ,且寄存器拥有复位清零功能,其复位又分为同步复位和异步复位. 。

使用按键控制LED灯,按键输入的信号输入给输出信号, 假如在某个时钟周期内输入信号产生了毛刺 : *对于组合逻辑,输出也会有毛刺 。

2.3 RTL 。

module filp_flop(

input wire sys_clk,

input wire sys_rst_n,

input wire key_in,

output reg led_out

);

// 同步复位

always@(posedge sys_clk)

if(sys_rst_n == 1'b0)

let_out <= 1'b0;

else

let_out <= key_in;

endmodule

module filp_flop(

input wire sys_clk,

input wire sys_rst_n,

input wire key_in,

output reg led_out

);

// 异步复位

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

let_out <= 1'b0;

else

let_out <= key_in;

endmodule

推荐使用异步复位 。

// 同步复位

`timescale 1ns/1ns

module tb_flip_flop();

reg sys_clk;

reg sys_rst_n;

reg key_in;

initial begin

sys_clk <= 1'b1;

sys_rst_n <= 1'b0;

key_in <= 1'b0;

#20;

sys_rst_n <=1'b1;

#210;

sys_rst_n <=1'b0;

#40;

sys_rst_n <=1'b1;

end

initial begin

$timeformat(-9,0,"ns",6);

$monitor("@time:%t:key_in=%b,led_out=%b",$time,key_in,led_out);

end

// 模拟系统时钟

always begin

#10;

sys_clk = ~sys_clk;

end

// 时钟周期是20ns,保证每次数据变化小于时钟周期,避免差生毛刺

always #20 key_in <= {$random} % 2;

flip_flop flip_flop_inst(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.key_in (key_in),

.led_out (led_out)

);

endmodule

最后此篇关于09-寄存器的文章就讲到这里了,如果你想了解更多关于09-寄存器的内容请搜索CFSDN的文章或继续浏览相关文章,希望大家以后支持我的博客! 。

我无法理解如何使用一些旧的 VGA 代码在这个示例中设置序列 Controller 寄存器: mov dx,SC_INDEX mov ax,0604h out dx,ax

我希望对 zmm 0-31 寄存器集的四字元素执行整数算术运算并保留这些运算产生的进位位。看来这只有在通用寄存器集中处理数据时才有可能。 因此,我想将信息从 zmm 0-31 寄存器之一复制到通用寄存

ARM 64中包含多种寄存器,下面介绍一些常见的寄存器。 1 通用寄存器 ARM 64包含31个64bit寄存器,记为X0~X30。 每一个通用寄存器,它的低32bit都可以被访问,记为W0~W

1.寄存器 组合逻辑存在一个最大的缺点就是存在竞争与冒险,系统会产生不定态;使用时序逻辑电路就会极大的改善这种情况 寄存器具有存储功能,一般是由D触发器构成,由时钟脉冲控制,每个D触发器能够

使用 $gp 是否存在危险?注册以存储值?我想我的问题是 $gp 的真正功能是什么?它是否以某种方式在幕后调用,以便如果我使用它,事情可能会变得非常非常错误? 最佳答案 那么,$gp register

我遇到了这段代码的问题,我无法弄清楚问题出在哪里。所以当我运行这段代码时:if $row["count"] > 0 else块运行和 $_SESSION["error"]设置。 当$row["coun

所以我正在做二进制炸弹的变体。这就是阶段 0x0000000000401205 : sub $0x8,%rsp 0x0000000000401209 : cmp $0x3,

我在一个名为 (EmployeeDetailKey - varchar(10)) 的字段中获得了一个值,其中包含顺序值,例如 00001, 00002, 00003.... 它位于 Employeed

我有一个要求,应该为每个调用的线程分配一个计数器变量。但我没有得到预期的结果,实际上计数器在线程中重复。我创建了一个虚拟表和一个过程来将计数器值插入到表中。无论如何,是否可以更改代码以便线程获得递增的

预期输出:需要打印第4季度的wage_amt +--------------+--------------+--------------+--------------+ | wages_amt_q1

如何匹配模式 abc_[someArbitaryStringHere]_xyz? 为了澄清,我希望正则表达式能够匹配以下性质的字符串: abc_xyz、abc_asdfsdf_xyz、abc_32rw

从下拉列表(自定义)中选择一个值而不是常规下拉列表,它有很多下拉值 我可以用代码选择第一个值 find('.selected', :text=>arg1,exact: false).click 但无法

这个问题不太可能帮助任何 future 的访问者;它只与一个小的地理区域、一个特定的时间点或一个非常狭窄的情况有关,这些情况并不普遍适用于互联网的全局受众。为了帮助使这个问题更广泛地适用,visit

我有 .csv 文件中的数据,它包含 2 列 x 轴和 y 轴。从 .csv 文件读取轴,然后使用拉伸(stretch)指数函数拟合数据,但显示错误。 这里我给出示例数据以方便理解。 我的函数是f(x

我正在尝试使用以下汇编代码将磁盘扇区加载到内存中,但正如我在终端中使用一些 int 0x10 时发现的那样,它不起作用的原因是它陷入了无限循环。我以为循环会自动为我递减 cx 寄存器。下面是代码,其中

我正在尝试编写一个脚本,该脚本将在 vim 中打开一个文件并将其中的特定行复制到 vim 的寄存器之一中。当脚本再次运行时,它会决定再次打开文件,然后将 vim 寄存器中的值粘贴回。实际上,脚本应该在

我目前正在尝试弄清楚如何将指针寄存器 SI 指向的内存中的第一个字节添加到 AX 寄存器的当前内容中。 因此,如果 SI 包含某个地址,并且该地址在内存中的值是:00 和 01,我希望将 00 添加到

我试图将两个 16 位数字与以下 NASM 代码相乘: mov ax, [input1] mov bx, [input2] mul bx 前面代码的结果存储在 DX:AX 我试图使用来自单独库“pri

我正在尝试修改 rip 寄存器(只是为了好玩)。 buffer 应该是内存地址,所以不知道为什么会得到Error: operand type mismatch for 'movq' #include

我可以告诉gcc-style inline assembly把我的__m512i变量到特定 zmm注册,如 zmm31 ? 最佳答案 就像在根本没有特定寄存器约束的目标(如 ARM)上一样,使用 lo

我是一名优秀的程序员,十分优秀!