作者热门文章

- Java锁的逻辑(结合对象头和ObjectMonitor)

- 还在用饼状图?来瞧瞧这些炫酷的百分比可视化新图形(附代码实现)⛵

- 自动注册实体类到EntityFrameworkCore上下文,并适配ABP及ABPVNext

- 基于Sklearn机器学习代码实战

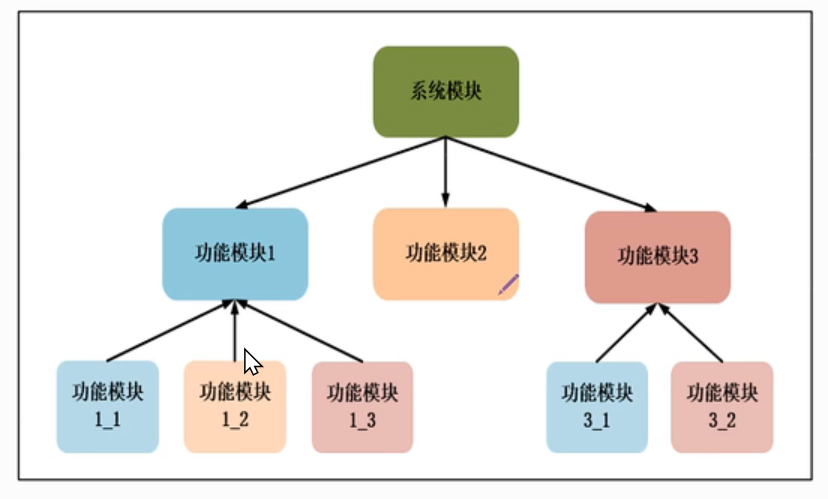

数字电路中根据模块层次不同有两种基本的结构设计方法: 自底向上的设计方法和自顶向下的设计方法 。

自底向上的设计是一种传统的设计方法,对设计进行逐次划分的过程是从存在的基本单元出发的(基本单元是已有的或者是购买的),有基本单元构建高层单元,依次向上,直至构建系统 。

从系统开始,把系统分为基本单元,然后再把每个单元划分为下一层次的基本单元,一直这样做下去,直到直接可以使用EDA元件库中的元件来实现为止 。

将顶层模块进行继续划分 。

module half_adder(

input wire in_1,

input wire in_2,

output wire sum,

output wire count

);

assign {count,sum} = in_1 + in_2;

endmodule

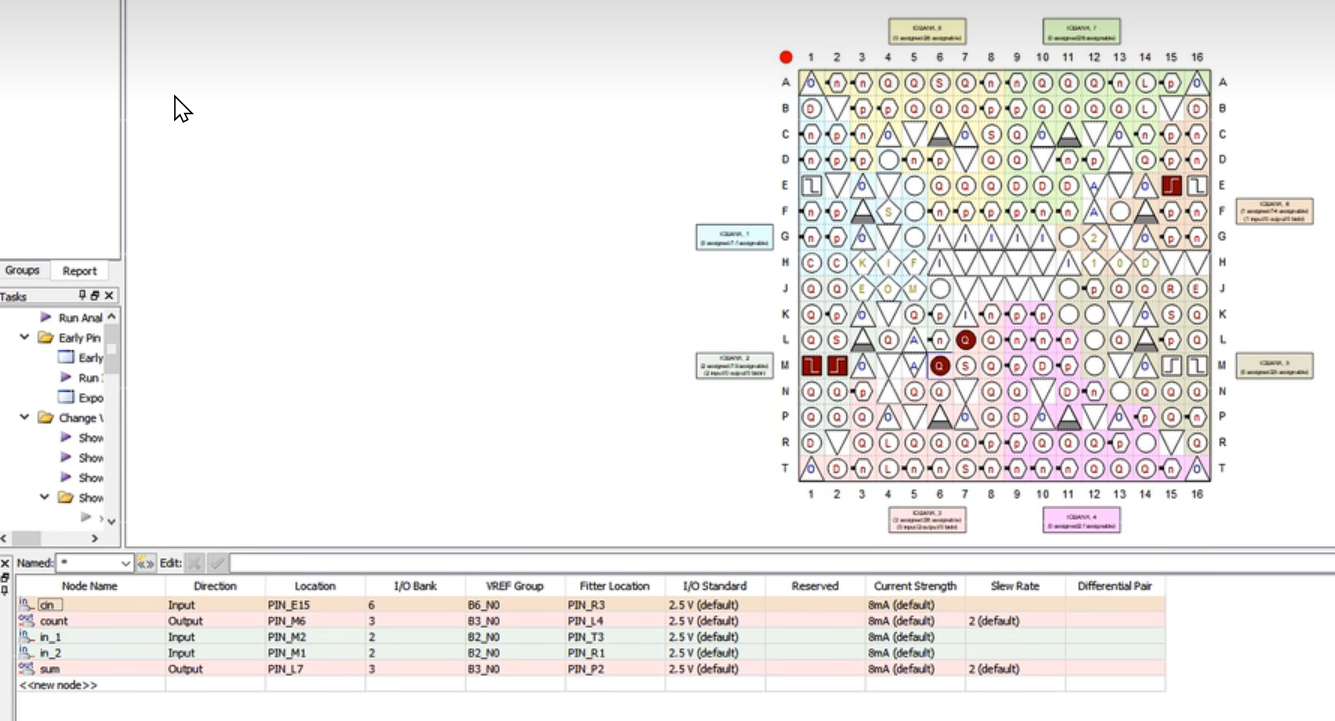

module full_adder(

input wire in_1, // 输入两个加数和一个低位进位

input wire in_2,

input wire cin,

output wire sum, // 输出和 进位

output wire count

);

// 例化过程中需要引出的线,单独进行命名

// 第一个半加器的输出 sum -- 顶层没有定义子模块的输出,所以要自己定义

// 声明两个变量,将第一个半加器的输出引出来

// 可以对变量进行重新进行命名

wire h0_sum;

wire h0_count;

// 将第二个半加器的输出引出来

wire h1_count;

half_adder half_adder_inst1(

.in_1 (in_1), // 输入in_1 in_2

.in_2 (in_2),

.sum (h0_sum), // in_1 ^ in_2

.count (h0_count) // in_1 & in_2

);

half_adder half_adder_inst2(

.in_1 (cin), // 输入是第一个半加器的输入和进位

.in_2 (h0_count),

.sum (sum), // 输出是 in_1 ^ in_2 ^ cin

.count (h1_count) // 进位是 (in_1 ^ in_2) & cin + in_1 & in_2

);

assign count = (h0_count | h1_count);

endmodule

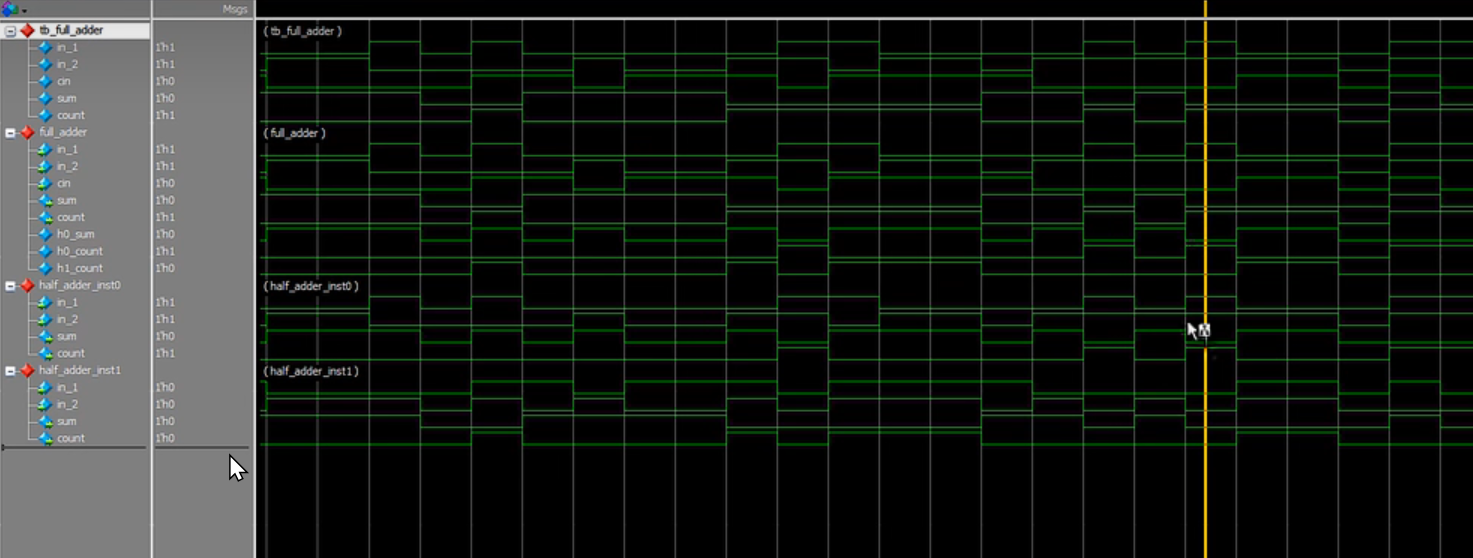

`timescale 1ns/1ns

module tb_full_adder();

reg in_1;

reg in_2;

reg cin;

wire sum;

wire count;

initial begin

in_1 <= 1'b0;

in_2 <= 1'b0;

cin <= 1'b0;

end

initial begin

$timeformat(-9,0,"ns",6);

$monitor("@time:time=%t,in_1=%b,in_2=%b,cin=%b,sum=%b,count=%b",$time,in_1,in_2,cin,sum,count);

end

always #10 in_1 = {$random} % 2;

always #10 in_2 = {$random} % 2;

always #10 cin = {$random} % 2;

full_adder full_adder_inst(

.in_1 (in_1),

.in_2 (in_2),

.cin (cin),

.sum (sum),

.count (count)

);

endmodule

最后此篇关于07-层次化设计--全加器的文章就讲到这里了,如果你想了解更多关于07-层次化设计--全加器的内容请搜索CFSDN的文章或继续浏览相关文章,希望大家以后支持我的博客! 。

我正在尝试将多个水平链接的 Button 和 TextView 垂直链接为 View 集,但仍保持平面 View 层次结构。这是我的初始布局和代码:

到目前为止,我已经在Google BigQuery上训练了几种模型,目前我需要查看模型的外观(即架构,损失函数等)。 有没有办法获取这些信息? 最佳答案 仔细阅读文档后,我可以说该功能尚不存在。我什至

本文实例讲述了PHP实现二叉树深度优先遍历(前序、中序、后序)和广度优先遍历(层次)。分享给大家供大家参考,具体如下: 前言: 深度优先遍历:对每一个可能的分支路径深入到不能再深入为止,而且每个

我是一名优秀的程序员,十分优秀!